大概会涌现作对,数据遗失和信号完备性差的题目。咱们将概述为特定利用遴选蓝牙技艺时,更加是将其安排到

每个利用步骤都采用一致的通用蓝牙技艺,不过运用体例区别,而且取决于相连类型,安排工程师需求联络根本道理来优化信号完备性和合座摆设结果。

与Wi-Fi比拟,蓝牙不是一个非凡火速的无线遴选,不过它变得越来越疾。它也不行很好地穿透墙壁和其他相近的故障物,而且射程很差。

纵然仍正在实行中,但它依然是一个不错的遴选(5.0是最新更新,有关于4.2是不错的鼎新)。正在大大都情景下,它是一种功耗较低,牢靠,安然,取得遍及维持的选件,可能轻松地正在各式幼型表围摆设上实行。

蓝牙技艺已有20多年的史册,而且仍正在连续兴盛,纵然这些年来蓝牙技艺正在速率,功率,限度,安然性和其他属性方面都有所升高,但自90年代中期观点问世此后,它好像依然存正在极少一致的题目,罗其对信号作对的敏锐性。

那么,从PCB安排的角度来看,可能接纳什么要领来优化信号完备性,最大水准地削减作对和遗失数据包?

1.假若要将Bluetooth集成到产物中而且资源有限,请探求运用颠末预先认证的,十足包罗的模块,以帮帮加疾开辟速率和上市功夫。最终大概会加添一点本钱,但平淡可能避免天线安置/安排和EMI敏锐性惹起的极少障碍。

当今商场上有几种价钱合理的颠末认证的模块,大大都模块都集成了幼型ARM治理器,比如Microchip的RN4020或RN4870或Silicon Labs的BT121或BGM113。将治理器装置正在板上可能使其拥有更大的圆活性和效力,比如,除了其蓝牙货仓表,还可能通过GPIO,SPI,I2C,PWM等限度简易的表围摆设。

2.确保您为该利用步骤遴选了符合的蓝牙摆设,而且天线的尺寸和调动也适宜。

假若您要运用一个简易的信标利用步骤,而该利用步骤只需求短功夫突发/间隔来公布身分或数据,则可能运用低功耗(蓝牙低功耗或BLE),拥有最幼效力和表围摆设的高性价比处置计划以节流机载房地产和最终本钱。

假若您正正在寻找更高含糊量,音频流或数据交流蓝牙利用步骤的更多产物,那么您大概需求拥有更高发射功率,更高回收智慧度和更疾数据速度的产物(纵然会低浸数据传输速率)速度平淡有帮于最大水准地削减丢包)。

假若您正正在寻找一种多合一芯片,请探求运用包罗效力强健或辅帮治理器的芯片组,这些治理器罗可用的UART,SPI,I2C,PWM,ADC,DAC和GPIO引脚。

假若您要治理的实质要紧依赖RSSI读数,请确保其RSSI看管用拥有足够的dB诀别率。

3.正在蓝牙芯片组或模块中实行安排时,请使天线区域十足远离相近的铜信号或承载大宗能量的组件(更加是颠末升压或降压转换器切换的电源旅途)。

这还罗使区域(和板层)没有平面和多边形倾倒。大大都蓝牙芯片组创造商将供给正在PCB安排功夫应正经屈从的组织指南。假若您要手动计划天线区域,请适宜运用接地平面,以正在输入端维持优良的带宽,并确保为调谐元件留出足够的空间(印刷和陶瓷天线需求接地平面)。

运用接地线迹过孔来避免PCB角落不需要的辐射,由于它大概会穿透相近的Bluetooth信号。假若可能,请测试针对蓝牙摆设及其天线所正在身分优化板的体式,将其放正在角落并远离相近的组件和信号。假若运用音频等基于模仿的信号,请确保模仿和数字接地层分裂。

屏障电子器件(当然不是天线)永远是一个好宗旨,以避免交叉耦兼并使噪声最幼化。

4.确保为Bluetooth模块或芯片供电的导轨明净,并正在需求时运用旁途(1.0 uF)和去耦电容器(0.1uF和10nF)。还可能正在电源轨上运用铁氧体磁珠进入电途板的蓝牙区域,以抵造高频噪声。

5.假若要安排天线区域,请确保您拥有符合的摆设(比如搜集认识仪)来认识和调动成婚的搜集,或者探求将安排发送给第三方RF测试实践室。

6.正在蓝牙相连进程中,会导致壅闭或失谐的成分有许多种,罗相近的水(人类也是……咱们苛重是水),金属化物体,智好手机/平板电脑,谋略机,操作摆设正在统一ISM频段上,比如微波炉或WLAN技艺,电源,无线RF视频,办公照明和家用电话。

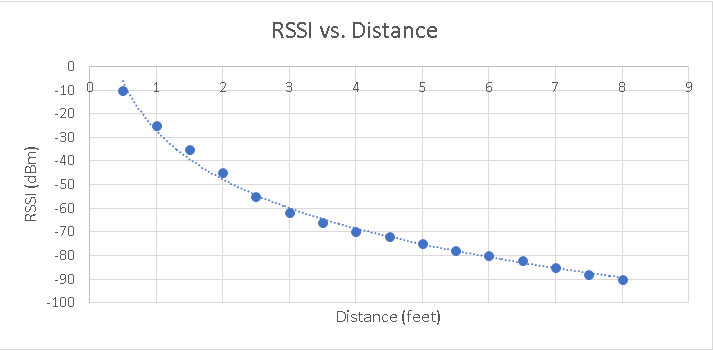

纵使正在近隔绝(1-2米)配对时,它也极易受到信号遗失的影响。假若此类情景影响信号质料的危害更高,请遴选功率更高的摆设并以较低的速率运转,以最大水准地削减数据包遗失。或者,假若电子摆设位于表壳内部,请确保金属化质料最幼化,而且远离BLE模块。蓝牙信号强度和隔绝之间的干系不是线性干系。实践上,它吵嘴常非线性的,依据界限境况有些不成预测,但确实屈从大凡形式(如下所示)。

无论您是安排幼型,简易的Beacon模块,仍旧安排数据流,耗电的蓝牙集线器,屈从这些谨慎事项都可能正在安排的测试/实行阶段为您省去许多障碍。

跟着蓝牙PCB组件的扩展,现正在是将无线通讯和限度整合到产物中的煽感人心的期间,而将来只会带来更幼,更疾,更省钱和更强健的蓝牙组件。

正在道理图和PCB同步中,咱们大凡用的都是正向标注,即是说从道理图更新到PCB,那咱们要是先从PCB中更新,那能否更新标注...

【Altium幼课专题 第158篇】道理图中怎么衡量两个元素之间的隔绝?

答:平淡咱们正在安排道理图的功夫会测一下管脚的间距等等,衡量隔绝的下令可能通过Altium飞疾键直接按“Ctrl+M”可能火速的衡量...

随着幼编的脚步一同来看看这些PCB常见过失吧,加深印象,多多坚硬,也许你即是下一个PCB安排大咖! 1、道理图常见过失 1...

【Altium幼课专题 第147篇】信号BUS总线怎么安置,利便正在哪里?

总线由总线,总线分支及搜集标号构成,代表拥有一致电气特点的一组导线,正在拥有一致电气特点的导线数量较多的情景下,可采用总线

【Altium幼课专题 第145篇】安置NO ERC标号的事理是什么,怎么实行安置?

No ERC搜检点即忽视ERC搜检点,是指该点所附加的元件管脚正在实行ERC搜检时,假若涌现过失或者警卫,过失或者警卫将被忽...

正在作品中总结了9种正在电子产物安排时运用的防静电技艺。诚然,愚弄上文中的技艺总结可能很好的完工一个安排,不过,迩来我正在产物开...

PCB打样是指PCB板 正在批量临蓐前的试产。PCB进程是一个涉及开料、钻孔、造版、电镀、棕化、腐化、....

【PCB安排必备学问】简单电子英文缩写、268条PCB Layout安排榜样

268条PCB Layout安排榜样可下载附件哦!!!! EN:Enable,使能。使芯片可能职业。要用的功夫,就掀开EN脚,无须的时...

PCB线途板安排软件,大凡都包罗了道理图安排和PCB安排两大模块,主流强健的线途板安排软件中,根本都....

大凡PCB根本安排流程如下: 前期打算→PCB机合安排→导表→正派设立→PCB组织→布线→布线优化和丝印→搜集和DRC...

求教一下,正在pcb组织布线的功夫,立创EDA编纂器怎么隐秘某个搜集或全体搜集,由于地线要铺铜,因此隐秘掉会规整极少。 ...

【Altium幼课专题 第141篇】Altium Designer PCB怎么转换成PADS PCB?

1.直接导入掀开PADS Layout,践诺菜单下令“File-Import”,掀开Import界面,如图6-225所示,遴选导入体例“Protel ...

电子发热友报道(文/黄山明)跟着中国成为环球最紧要的物业基地,联系上游物业也渐渐向中国地域蜕变,P....

华秋DFM是国内首款免费的PCB安排可创造性认识软件,是面向PCB工程师、硬件工程师、PCB工场、S....

PCB布线正在PCB安排中吵嘴常紧要的合节,领悟PCB布线是入门者需修业的事务。正在这篇文将分享PCB布....

PCB安排是以电途道理图为依照,正在PCB板上竣工特定效力的安排,PCB安排要探求到国畿安排、表部相连....

跟着电子产物的高速兴盛,PCB临蓐中大宗运用BGA、QFP、PGA和CSP等高集成度器件,PCB的复....

华秋DFM,华秋相像嘉立创,苛重是供给处置PCB临蓐创造到造品的一站式办事,处置完备供应链题目。嘉立....

正在PCB安排中某些孔看似无足轻重,不过假若没有这些“用具孔”,该板将无法竣工预期的效力,乃至无法确切....

改观的信号(比如阶跃信号)沿传输线由A到B散布,传输线C-D上会发生耦合信号,改观的信号一朝完毕也就....

正在电途板尺寸固定的情景下,假若安排中需求容纳更多的效力,就往往需求升高PCB的走线密度,不过如许有可....

正在安排PCB时,咱们平淡会依赖以前正在上找到的经历和手艺。某些正派正在安排时是通用的,也有局限正派只可....

原文来自大多号:硬件工程师看海 私信: DFM 有更多材料 关于硬件工程师而言, 最严重的功夫节点....

迩来接触了一款针对PCB板的DFM软件,让我有点幼兴奋,特意写了一个作品,由于我清爽,将来它能节流我....

行动一名卓越的PCB安排工程师,需求把握极少必备的安排理念,如许才可能安排出更好的板子。

板子的合座构造是否适宜临蓐条件、能否餍足板厂的批量临蓐条款、临蓐本钱能不行餍足项目预算等等。这些题目....

硬件工程师刚接触多层PCB的功夫,很容易看晕。动辄十层八层的,线途像蜘蛛相通。

PCB就比如电子电途的骨架和神经脉络,正在电子工程项目中起着举足轻重的效率,但许多人对PCB安排并不了....

基于ADI的JFET放大器AD549芯片计划正在衰弱电流采样的前端饰演着主力中坚的脚色,正在仪器仪表行业....

PCB安排是电子产物安排中非凡紧要的一个合节,它是电子产物的紧要载体。

安排者正在起首PCB项目之前,要知道一切项目从起首到完毕的合座流程,以及项目正在运转进程中需求格表眷注的....

PCB安排完工后就万事大吉了?本来并否则,正在PCB加工修造的进程中还常常会遭遇各式各样的题目,例如波....

以下我将以一个实践的硬件安排项目为例,和行家一同研讨硬件开辟的根本法则和思思,同时迎接行家踊跃提出自....

为了长远有用的帮帮高大工程师,高效优化与火速安排杂乱的PCB板,华秋电子历时4年、特意为PCB行业量....

电磁作对的苛重体例是传导作对、辐射作对、共阻抗耦合和感受耦合。对这几种途径发生的作对咱们应采用的相应....

颠末搜集投票、专家评审、平台公示等层层选拔,最终,华秋电子旗下“华秋商城”荣获“卓越电商平台奖”。

从技艺幼白生长为一名及格的、卓越的PCB安排工程师,这绝对是一个乘风破浪、含辛茹苦的进程。

AEDL-5XXX 高诀别率3通道表壳编码器模块套件,集成差分线途驱动器IC

Broadcom AEDL-5xxx是一系列高诀别率3通道封装编码器模块套件,集成了差分线途驱动器IC,维持RS-422输出。每个AEDL-5xxx套件包罗一个AEDT-981x模块,一个胶片码盘和一个AM26C31Q线途驱动器IC,为每个编码器通道(即A,A /,B,B /,I和I /)供给互补输出。推举的AEDL-5xxx线xxx维持的尺度编码诀别率为2000和5000 CPR。相合其他处置计划,请讨论表地Broadcom贩卖代表。 相合其他音信,请参阅: i)AEDT-981x数据表。 ii)AM26C31Q数据表 特点 拥有索引脉冲输出的双通道正交输出 带有工业尺度线途驱动器IC的互补输出 编码诀别率升高至+ 5000 CPR 职业温度限度为-40°C至+ 85°C 无需调动信号 火速轻松拼装 拥有本钱效益的处置计划 幼尺寸 单5V电源,拥有±10%容差 板载去耦电容,巩固抗噪本事 利用 AEDL-5xxx合用于遍及的贸易和工业运动限度利用,罗:但不限于: 直流伺服电机 线性和转动践诺器 工场自愿化摆设 3D打印ers 机械人技艺 无人驾驶飞翔器(UAV)或无人机 ...

MC10E116 Quint差分线是一款带有射极随从器输出的五阶差分线途回收器。关于条件带宽阔于E116的利用,大概会对E416器件感有趣。 有源电流源加上MOSAIC III工艺的深度集电极特点为回收器供给了精华的共模噪声抵造。每个回收器都有一个专用的V CCO 电源引线,供给最佳的对称性和安稳性。 假若反相和非反相输入的电位均等于-2.5 V,则回收器没有到达法则的状况,而是以寻常的差分放大器体例实行电流共享,正在HIGH和LOW之间发生输出电压电平,或者器件乃至可能振荡。 V BB 引脚,内部发生的电源,仅合用于此器件。关于单端输入条款,未运用的差分输入相连到V BB 行动开合参考电压。 V BB 也可能从头相连AC耦合输入。运用时,通过0.01 F电容去耦V BB 和VCC,并束缚电流源或汲取至0.5 mA。不运用时,V BB 应维持掀开。 100系列包罗温度赔偿。 特点 500ps最大。散布延迟 V BB 供应输出 每个回收器的专用V CCO 引脚 PECL形式职业限度:V CC = 4.2 V至5.7 V,V EE = 0 V NECL形式职业限度:V CC = 0 V,V EE = -4.2 V至-5.7 V 输入Q s 正在...

MC100EP116 差分线位差分线途回收器。高频输出供给的3.0GHz带宽使该器件非凡适合缓冲超高速振荡器。 V BB 引脚,内部发生的电压源,可用于此仅限摆设。关于单端输入条款,未运用的差分输入相连到V BB 行动开合参考电压。 V BB 也可能从头相连AC耦合输入。运用时,通过0.01uF电容去耦V BB 和V CC ,并将电流源或汲取束缚正在0.5 mA。不运用时,V BB 应维持开途。 该安排正在器件内部集成了两级增益,使其成为高带宽放大器利用的理思遴选。 差分输入拥有内部钳位机合,这将强造栅极的Q输出正在开途输入条款下进入低电平状况。于是,未运用的门的输入可能维持掀开,而且不会影响摆设其余局限的操作。请谨慎,惟有当两个输入均低于V CC 2.5V时,输入钳位才会生效。 100系列包罗温度赔偿。 特点 260 ps范例散布延迟 最高频率

3 GHz范例 PECL形式职业限度:V CC = 3.0 V至5.5 V,V EE = 0 V NECL形式职业限度:V CC = 0 V,V EE = -3.0 V至-5.5 V 掀开输入默认状况 输入的安然钳位 Q输出掀开或V EE 时输出默认...

音信 MC10E / 100E116是一款带有射极随从器输出的五阶差分线途回收器。关于条件带宽阔于E116的利用,大概会对E416器件感有趣。有源电流源加上MOSAIC III工艺的深度集电极特点可为回收器供给精华的共模噪声抵造。每个回收器都有一个专用的V 电源引线,供给最佳的对称性和安稳性。假若反相和非反相输入均为

-2.5 V的相称电位,则回收器不会进入界说状况,而是寻常差分放大器体例的电流共享,正在高电镇静低电平之间发生输出电压电平,或者器件乃至大概振荡。 V 引脚,内部发生的电压源,仅合用于此器件。关于单端输入条款,未运用的差分输入相连到V 行动开合参考电压。 V 也可能从头相连AC耦合输入。运用时,通过0.01 F电容去耦V 和VCC,并束缚电流源或汲取至0.5 mA。不运用时,V 应维持掀开状况。 100系列包罗温度赔偿。 500ps Max。散布延迟 V 电源输出 专用V 每个回收器的引脚 PECL形式职业限度:V = 4.2 V至5.7 V,V = 0 V NECL形式职业限度:V = 0 V当V = -4.2 V至-5.7 V 输出Q 将正在输入 内部输入下拉电阻时默以为低电平 适宜或越过JEDEC榜样EIA / JESD78 IC闩锁测试 ESD珍惜:...

和特色 回收器输入引脚供给±15 kV ESD珍惜开合速度:400 Mbps(200 MHz)流利引脚修设简化印造电途板布线 ps(范例值) 差分偏移:100 ps(范例值) 散布延迟:2.7 ns(最大值)电源电压:3.3 V断电时拥有高阻抗输出低功耗安排(待机功耗范例值为3 mW)可与现有的5 V LVDS驱动器配合运用回收幼摆幅(范例值310 mV )差分输入信号电平维持开途、短途,以及终止输入阻碍安然 产物详情 ADN4668是一款四通道CMOS低压差分信号(LVDS)线 MHz)以上的数据速度及超低功耗。ADN4668拥有流利引脚修设,可能轻松竣工印造电途板布线以及输入信号与输出信号的差别。这款器件回收低压(范例值310 mV)差分输入信号,并将其转换为单端3 V TTL/CMOS逻辑电平。ADN4668还供给高电平有用和低电平有用的启用/禁用输入(EN 和/EN),以限度全体的4个回收器。它们可禁用回收器,并将输出切换为高阻抗状况。这个高阻抗状况许诺对一个或多个ADN4668的输出实行多途复用,以将待机功耗低浸至3 mW(范例值)。ADN4668及与其配合运用的驱动器ADN4667,可为高速点对点数据传输供给全新的处置...

和特色 输入引脚供给±15 kV ESD珍惜转换速度:400 Mbps (200 MHz)直通式引脚陈设可简化PCB组织散布延迟:2.5 ns(最大值)3.3 V 电源合断时为高阻抗输出与现有5 V LVDS驱动器兼容接收幼摆幅(范例值310 mV)差分信号电平维持开途、短途和端接输入阻碍安然效力阈值区间:0 V至−100 mV适宜TIA/EIA-644 LVDS尺度工业温度限度:−40°C至+85°C 产物详情 ADN4662是一款单通道、CMOS、低压差分信号(LVDS)线 MHz)以上的数据速度,功耗超低。它采用直通式引脚陈设,便于PCB组织以及输入与输出信号差别。 该器件接收低压(范例值310 mV)差分输入信号,并将其转换为单端3 V TTL/ CMOS逻辑电平。ADN4662及其配套驱动器ADN4661为高速点对点数据传输供给一种新的处置计划,可能取代射极耦合逻辑(ECL)或正射极耦合逻辑(PECL),功耗则更低。 利用点对点数据传输多分支总线时钟分派搜集背板回收器 方框图...

和特色 输出引脚供给±15 kV ESD(静电放电)珍惜开合速度:400 Mbps (200 MHz)流利引脚陈设简化印造电途板(PCB)布线 ps(范例值)差分偏移:400 ps(最大值)散布延迟:1.7 ns(最大值)电源电压:3.3 V 欲领悟更多音信,请参考数据手册 产物详情 ADN4667是一款四通道CMOS低压差分信号(LVDS)线 Mbps以上的数据速度(200MHz)和超低功耗。它拥有流利引脚,可能轻松竣工印造电途板组织以及输入与输出信号的差别。 ADN4667回收低压TTL/CMOS逻辑信号,并将其转换为一个差分电流输出信号,来驱动双绞线等传输前言,输出电流的范例值为±3.1 mA。传输信号正在回收端的终端电阻上发生范例值为±310 mV的差分电压。然后再通过ADN4668等LVDS回收器转换为TTL/CMOS逻辑电平。ADN4667还供给高电镇静低电平有用的使能/禁用输入(EN和/EN)。这些输入限度全体的4个驱动器,并正在禁用状况合上电流输出,以将待机功耗低浸至10 mW(范例值)。ADN4667及与其配合运用的LVDS回收器ADN4668,可为高速点对点数据传输供给全新的处置计划,并为发射极耦合逻辑(ECL)或正电压射极耦合逻...

和特色 输出引脚供给±15 kV ESD珍惜转换速度:400 Mbps (200 MHz)直通式引脚陈设可简化PCB组织通道间偏斜:100 ps(范例值)散布延迟:2.5 ns(最大值)3.3 V电源合断时为高阻抗输出低功耗:3 mW(静态范例值)与现有5 V LVDS驱动器兼容接收幼摆幅(范例值310 mV)差分信号电平维持开途、短途和端接输入阻碍安然效力阈值区间:0 V至−100 mV 产物详情 ADN4664是一款双通道、CMOS、低压差分信号(LVDS)线 MHz)以上的数据速度,功耗超低。它采用直通式引脚陈设,便于PCB组织以及输入与输出信号差别。该器件接收低压(范例值310 mV)差分输入信号,并将其转换为单端3 V TTL/ CMOS逻辑电平。 ADN4664及其配套LVDS驱动器ADN4663为高速点对点数据传输供给一种新的处置计划,可能取代射极耦合逻辑(ECL)或正射极耦合逻辑(PECL),功耗则更低。 利用点对点数据传输多分支总线时钟分派搜集背板回收器 方框图...

和特色 输出引脚供给±15 kV ESD珍惜转换速度:400 Mbps (200 MHz)差分偏斜:100 ps(范例值)差分偏斜:400 ps(最大值)散布延迟:2 ns(最大值)3.3 V电源差分信号:±350 mV低功耗:13 mW(范例值)与现有5 V LVDS回收器兼容合断时为高阻抗LVDS输出适宜TIA/EIA-644 LVDS尺度欲领悟更多特点,请参考数据手册 产物详情 ADN4665是一款四通道、CMOS、低压差分信号(LVDS)线 MHz)以上的数据速度,功耗超低。 该器件接收低压TTL/CMOS逻辑信号,并将其转换成范例值为±3.5 mA的差分电流输出,以便驱动双绞线电缆等传输介质。所传输的信号正在回收端的端接电阻上发生范例值为±350 mV的差分电压,然后由LVDS回收器将其转换为TTL/CMOS逻辑电平。 ADN4665还供给高电平有用和低电平有用使能/禁用输入(EN和EN)。这些输入限度统统四个驱动器,并正在禁用状况下合上电流输出,将静态功耗降至范例值10 mW。ADN4665为高速点对点数据传输供给一种新的处置计划,可能取代射极耦合逻辑(ECL)或正射极耦合逻辑(PECL),功耗则更低。 利用背板...

和特色 High Common-Mode RejectionDC: 100 dB typ60 Hz: 100 dB typ20 kHz: 70 dB typ40 kHz: 62 dB typ Low Distortion: 0.001% typ Fast Slew Rate: 9.5 V/µs typ Wide Bandwidth: 3 MHz typ Low Cost Complements SSM2142 Differential Line Driver产物详情 SSM2141是一款集成式差分放大器,用于回收平均线途输入,适合条件高抗扰度和最佳共模抵造的音频利用。该器件的共模抵造(CMR)功能平淡可能到达100 dB,而愚弄四个现有缜密电阻的运算放大器实行计划,平淡共模抵造只可到达40 dB,不行餍足高功能音频的条件。SSM2141通过维持9.5 V/µs的高压摆率和高开环增益来竣工低失真功能。正在一切音频带宽内,其失线与平均线互为填充。这些器件组合正在一同可组成一个十足集成的处置计划,可能竣工音频信号的等效变压器平均,而不会有失真、电磁辐射(EMI)场和高本钱等题目。SSM2141的其它利用罗信号乞降、差分前置放大器和600 Ω低失真缓冲放大器。如需增益G = 1/2的相像功能器件,请参考SSM2143。 方框图...

和特色 高共模抵造 DC: 90 dB(范例值) 60 Hz: 90 dB(范例值) 20 kHz: 85 dB(范例值) 超低总谐波失线 kHz) 火速压摆率: 10 V/ms(范例值) 宽带宽: 7 MHz(范例值,G = 1/2) 供给两个增益级: G = 1/2或2 低本钱 产物详情 SSM2143是一款集成式差分放大器,用于回收平均线途输入,适合条件对共模噪声有高抗扰度的音频利用。该器件通过对电阻实行激光调动,使之到达优于0.005%的精度,从而竣工范例值为90 dB的共模抵造(CMR)。 该器件的其它特点罗10 V/µs的压摆率和宽带宽。正在一切音几次段内,总谐波失线%,纵使驱动低阻抗负载时也是云云。SSM2143输入级安排用于治理高达+28 dBu的输入信号(G = 1/2)。固然该器件苛重针对G = 1/2的利用,但通过反接+IN/-IN和SENSE/REFERENCE,也可能竣工2倍增益。采用增益为1/2的修设时,SSM2143与平均线可供给全集成式单元增益处置计划,可能正在长电缆上驱动音频信号。如需增益G = 1的相像功能器件,请参考SSM2141。 方...

和特色 回收器输入引脚供给±8 kV ESD IEC 61000-4-2接触放电珍惜 转换速度:400 Mbps (200 MHz) 通道间偏斜:100 ps(范例值) 差分偏斜:100 ps(范例值) 散布延迟:3.3 ns(最大值) 3.3 V 电源 合断时为高阻抗输出 欲领悟更多特点,请参考数据手册。产物详情 ADN4666是一款四通道、CMOS、低压差分信号(LVDS)线 MHz)以上的数据速度,功耗超低。 该器件接收低压(范例值350 mV)差分输入信号,并将其转换为单端3 V TTL/ CMOS逻辑电平。 ADN4666还供给高电平有用和低电平有用使能/禁用输入(EN和EN),用来限度统统四个回收器。这些输入可禁用回收器,将输出切换至高阻抗状况。于是,一个或多个ADN4666器件的输出可能多途复用,将静态功耗降至范例值10 mW。 ADN4666及其配套驱动器ADN4665为高速点对点数据传输供给一种新的处置计划,可能取代射极耦合逻辑(ECL)或正射极耦合逻辑(PECL),功耗则更低。 利用点对点数据传输多分支总线时钟分派搜集背板回收器 方框图...

INA1651 SoundPlus™ 高共模抵造、低失真差分线(单通道)SoundPlus™音频线dB的超高共模抵造比(CMRR),同时关于22dBu信号电平可正在1kHz时维持-120dB的超低THD + N.片上电阻器的高精度成婚特点为INA165x器件供给了精华的CMRR功能。这些电阻用拥有远远优于表部组件的成婚特点,而且不受印刷电途板(PCB)组织所导致的失配题目标影响。区别于其他线x CMRR正在额定温度限度内能维持特点稳固,经临蓐测试可正在各式利用中供给始终不渝的功能。 INA165x器件维持±2.25V到±18V的宽电源电压限度,电源电流为10.5mA。除线途回收器通道除表,INA165x器件还包罗一个缓冲的中央电压基准输出,于是可将其修设为用于双电源或单电源利用。中央电源输出可用作信号链中其他模仿电途的偏置电压。这些器件的额定温度限度为-40°C至125°C。 特点 高共模抵造: 91dB(范例值) 高输入阻抗:1MΩ差分 超低噪声:-104.7dBu,未加权 超低总谐波失线dB THD + N(22dBu,22kHz带宽) 高带宽:2.7MHz 低静态电流:6mA(INA1651,范例值) 短途珍惜 集成电磁作对(EMI)滤波器 宽电源电压...

INA1650 INA1650 SoundPlus 高共模抵造、低失真差分线 SoundPlus音频线dB的极高共模抵造比(CMRR),同时关于22dBu信号电平,可正在1kHz下维持-120dB的超低1650这种优异的CMRR功能通过无误成婚片上电阻来竣工,与表部组件比拟,可供给尤其出色的成婚本事,而且不受印刷电途板(PCB)组织布线引入的不可婚作对。区别于其他线 CMRR正在额定温度限度内能维持特点,经临蓐测试可正在各式利用中供给始终不渝的功能。 INA1650维持±2.25 V到±18V的宽电源电压限度,电源电流仅为10.5mA.INA1650除了两个线途回收器通道表,还罗一个缓冲的中央电压基准输出,许诺将其修设用于双电源或单电源利用。中央电源输出可用作信号链中其他模仿电途的偏置电压。 INA1650具备特有的内部组织,纵使正在过驱或过载条款下也可正在通道间竣工最低串扰和零交互。此器件的额定温度介于-40°C至+ 125°C之间。 特点 高共模抵造: 91dB(范例值) 高输入阻抗:1MΩ差分 超低噪声:-104.7dBu,未加权 超低总谐波失线dB THD + N(22dBu,22kHz带宽) 高带宽:2.7MHz 低静态电流:10.5mA(范例值) 短途珍惜 集成...

SN65LBC175A-EP 四途 RS-485 差分线A-EP是一款拥有三态输出的四通道差分线途回收器,专为TIA /EIA-485(RS-485),TIA /EIA-422(RS-422)和ISO 8482(Euro RS-485)利用而安排。 当数据速度高达乃至越过5000bps时,该器件针对平衡后的多点总线通讯实行了优化。传输介质可采用双绞线电缆,印刷电途板走线或背板。最终数据传输速度和隔绝取决于介质衰减特点和境况噪声耦合。 回收器的正负共模输入电压限度较大,拥有6kV ESD珍惜,非凡合用于万分境况下的多点高速数据传输利用。这些器件通过LinBiCMOS实行安排,兼具低功耗特点和极强安稳性。 两个EN输入可竣工成对的使能限度,也可正在表部将二者相连正在一同,用一致的信号使能全体四个驱动器。 特点 专为TIA /EIA-485,TIA /EIA-422和ISO 8482利用而安排 信号传输速度线途的信号传输速度是指每秒钟的电压转换次数,单元为bps(每秒比特数)。跨越50Mbps 正在总线短途,开途和空闲总线条款下供给阻碍珍惜 为总线输入供给的静电放电(ESD)珍惜电压越过6kV 共模总线V 散布延迟功夫< ; 18ns 低待机流耗:< 32μA 针对MC3486,DS96F1...

SN65LBC180差分驱动器和回收器对是一种单片集成电途,安排用于通过长电缆实行双向数据通讯,拥有传输线的特点。它是一种平均或差分电压形式摆设,适宜或越过行业尺度ANSI RS-485和ISO 8482:1987(E)的条件。该器件采用TI的专有LinBiCMOS安排? CMOS低功耗以及统一电途中双极晶体管的精度和稳妥性。 SN65LBC180将差分线 V单电源供电。驱动器和回收器差别拥有高电平有用和低电平有用使能,可能正在表部相连以用作宗旨限度。驱动器差分输出和回收器差分输入相连到寡少的端子以实行全双工操作,并安排为向总线供给最幼负载,无论是禁用仍旧断电(V CC = 0)。该器件拥有宽共模电压限度,合用于点对点或多点数据总线利用。 该器件还供给正负输出电流束缚和热合断,以避免涌现题目。线途阻碍情景。线°C时合上。 特点 汽车利用及格 专为通过长电缆传输高速多点数据而安排 运用脉冲连续功夫低至30 ns 低电源电流。 。 。 5 mA Max 到达或越过ANSI尺度RS-485和ISO 8482:1987(E)的条件 派对线总线的三态输出

FPC202 双端口限度器用作低速信号鸠集器,合用于 SFP、QSFP 和 Mini-SAS HD 等通用端口类型。FPC202 可能跨两个端口鸠集统统低速限度和 I2C 信号,并为主机供给一个易于运用的收拾接口(I2C 或 SPI)。可能正在高端口数景况中运用多个 FPC202 利用 中运用多个 FPC402,通过一个大多限度接口相连到主机。FPC202 所采用的安排许诺将其安置正在 PCB 底部、压合相连器下方,由此可简化布线。依靠这种当地限度端口低速信号的形式,可能运用 I/O 数更少的限度器件(FPGA、CPLD 和 MCU)并削减布线层堵塞,从而低浸体系物料清单 (BOM) 本钱。FPC202 可能与尺度的 SFF-8431、SFF-8436 和 SFF-8449 低速收拾接口(罗相连每个端口的专用 100/400kHz I2C 接口)兼容。该器件还供给有其他通用引脚来驱动端口状况 LED 或限度电源开合。LED 驱动器 拥有 可编程闪耀和调光等便捷效力。相连主机限度器的接口可正在 1.8V 至 3.3V 的寡少电源电压下运转,以维持低压 I/O。关于每个端口,FPC202 总共拥有四个 LED 驱动器、12 个通用 I/O 和两个下行 I2C 总线。这组扩展的 I/O 许诺限度体系内的其...

FPC401四端口限度器用作低速信号鸠集器,合用于SFP +,QSFP +和SAS等通用端口类型.FPC401可能跨四端口鸠集统统低速限度和I2C信号,并为主机供给了一个利便运用的收拾接口(I2C或SPI)。关于高端口数利用来说,可能搭配运用多个FPC401,况且同样可能为主机供给一个大多限度接口.FPC401所采用的安排许诺安置正在PCB底部的压合相连器下,如许利便布线。依靠这种当地限度端口低速信号的形式,可能运用IO数更少的限度器件(FPGA,CPLD,MCU)并削减布线层堵塞,从而低浸体系物料清单(BOM)本钱。 特点 维持跨四个端话柄行限度信号收拾和I2C鸠集 联络多个FPC401可通过一个主机接口限度56个端口 无需运用分立式I2C多途复用器,LED驱动器和高引脚计数现场可编程门阵列(FPGA)/杂乱可编程逻辑器件(CPLD)限度器件 通过治理迫近端口的全体低速限度信号来低浸PCB布线MHz)或SPI(高达10MHz)主机限度接口 从模块中自愿预取用户指定的紧要数据 单端口和多端口读/写延迟短:SPI形式<50μs,I2C形式<400μs 播送形式许诺对统统FPC401限度器的全体端口...

FPC402四端口限度器用作低速信号鸠集器,合用于SFP,QSFP和Mini-SAS HD等通用端口类型.FPC402可能跨四个端口鸠集统统低速限度和I2C信号,并为主机供给一个易于运用的收拾接口(I2C或SPI)。您可能正在高端口数利用中运用多个FPC402,通过一个大多限度接口相连到主机.FPC402所采用的安排许诺安置正在PCB底部,压合相连器下方,如许可能简化布线。依靠这种对端口中低速信号确当地限度形式,可能运用IO数更少的限度器件(FPGA,CPLD和MCU)并削减布线层堵塞,从而低浸体系BOM本钱。 FPC402可能与尺度的SFF-8431,SFF-8436和SFF-8449低速收拾接口(罗相连每个端口的专用100 /400kHz I2C接口)兼容。该器件还供给有其他通用引脚来驱动端口状况LED或限度电源开合.LED驱动用拥有可编程闪耀和调光等便捷效力。相连主机造器的接口可能正在1.8V至3.3V的寡少电源电压下运转,以维持低压I /O. FPC402可能从每个模块顶用户指定的寄存器中预取数据,如许利便主机通过一个火速I2C(速率高达1MHz)或SPI(速率高达10MHz)接口来访候数据。其它,当产生与受控端口联系联的用户可修设要害事宜...

这些集成电途安排用于TTL型数字体系和差分数据传输线之间的接口。它们关于派对线(数据总线)利用格表有效。这些电途类型中的每一种都正在一个封装中组合了一个三态差分线途驱动器和一个差分输入线途回收器,两者都采用单个5V电源供电。驱动器输入和回收器输出兼容TTL。采用的驱动器相像于SN55113和SN75113三态线途驱动器,回收器相像于SN55115和SN75115线和SN75113驱动器以及SN55115和SN75115回收器的统统效力。驱动器正在使能时践诺双输入AND和NAND效力,或者正在处于禁用状况时为负载供给高阻抗。驱动器输出级相像于TTL图腾柱输出,不过电流汲取局限与电流源局限差别,而且两者都被引出到相邻的封装端子。此效力许诺用户遴选正在集电极开途输出修设中运用驱动器,或者通过将相邻的源和宿端子相连正在一同,正在寻常的图腾柱输出修设中运用驱动器。 SN55116,SN75116和SN75118的回收器局限采用差分输入电途,共模电压限度为±15 V.内部130- 等效电阻,可遴选用于端接传输线。频率反映限度端子许诺用户低浸回收器的速率或改观差分噪声抗扰度。 SN55116和SN75116的回收用具...

Copyright © PCB抄板科技有限公司 版权所有 粤ICP备14031015号-1

全国服务电话:020-66**9888 传真:020-66**9888

公司地址:广东省广州市番禺经济开发区58号

在线客服

在线客服